# **Technical Reference**

# **Tektronix**

**DPOJET Opt. PCE**

**PCI Express® Measurements & Setup Library**

Methods of Implementation (MOI) for Verification, Debug and Characterization

077-0267-00

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

TEKTRONIX, TEK and RT-Eye are registered trademarks of Tektronix, Inc.

### **Contacting Tektronix**

Tektronix, Inc. 14200 SW Karl Braun Drive or P.O. Box 500 Beaverton, OR 97077 USA

For product information, sales, service, and technical support:

- In North America, call 1-800-833-9200.

- Worldwide, visit www.tektronix.com to find contacts in your area.

## **Table of Contents**

| 1 | Intr | oduction to the DPOJET PCI Express Setup Library       | 2  |

|---|------|--------------------------------------------------------|----|

| 2 | PCI  | Express Specifications                                 | 3  |

|   | 2.1  | Differential Transmitter (TX) Output Specifications    | 3  |

|   | 2.2  | Differential Receiver (RX) Input Specifications        | 3  |

|   | 2.3  | Add-In Card Transmitter Path Compliance Specifications | 5  |

|   | 2.4  | System Board Transmitter Path Specifications           | 7  |

|   | 2.5  | PCI ExpressModule <sup>TM</sup> Specifications         | 9  |

|   | 2.6  | PCI Express External Cabling Specifications            | 12 |

|   | 2.7  | PCMCIA ExpressCard <sup>TM</sup> Specifications        | 14 |

| 3 | PCI  | Express Library Contents                               | 16 |

| 4 | Pre  | paring to Take Measurements                            | 17 |

|   | 4.1  | Required Equipment                                     | 17 |

|   | 4.2  | Probing Options for Transmitter Testing                | 18 |

|   |      | SMA Input Connection                                   | 18 |

|   |      | ECB pad connection                                     | 19 |

|   |      | Dual Port Connection                                   | 20 |

|   | 4.3  | Running the Test                                       | 21 |

| 5 | Par  | ameter Definitions and Method of implementation        | 23 |

|   | 5.1  | UI (Unit Interval) MOI                                 | 23 |

|   | 5.2  | TX Differential Pk-Pk Output Voltage MOI               | 24 |

|   | 5.3  | TX De-Emphasis Ratio                                   | 25 |

|   | 5.4  | TX Minimum Pulse Width MOI                             | 26 |

|   | 5.5  | TX Rise/Fall Time Mismatch MOI                         | 27 |

|   | 5.6  | Minimum TX Eye Width MOI                               | 28 |

|   | 5.7  | TX Median-to-Max Jitter MOI                            | 29 |

# 1 Introduction to the DPOJET PCI Express Setup Library<sup>1</sup>

This document provides the procedures for making PCI Express measurements with Tektronix DPO/DSA70000 Series Oscilloscopes with DPOJET (Jitter and Eye Analysis Tools) and probing solutions.

DPOJET and its PCI Express Setup Library provide transmitter path measurements (amplitude, timing, and jitter), waveform mask, and limits testing described in multiple variants of the PCI Express specifications.

Table 1 – Supported Specifications in the DPOJET Setup Library

| Test Methods | Spec<br>Revision | PCI Express Specification Title | Test Points Defined                                                             |

|--------------|------------------|---------------------------------|---------------------------------------------------------------------------------|

| Rev1.1       | Rev 1.1          | Base Specification              | Transmitter & Receiver (Section 4.3)                                            |

|              | Rev 1.1          | CEM Specification               | System and Add-In Card (Section 4.7) Reference Clock (Section 2.1)              |

|              | Rev 1.0          | Express Module Specification    | Transmitter Path and System Board (Section 5.4)                                 |

|              | Rev 1.0          | PCMCIA Express Card Standard    | Host System Transmitter Express Card Transmitter (Section 4.2.1.2)              |

| Rev2.0       | Rev 1.0          | External Cabling Specification  | Transmitter and Receiver Path (Section 3.3)                                     |

|              | Rev 2.0          | Base Specification              | Transmitter & Receiver (Section 4.4) Mobile Low Power Transmitter (Section 4.4) |

|              | Rev 2.0          | CEM Specification               | System and Add-In Card (3.5 & 6dB DeEmphasis) (Section 4.7)                     |

| Rev3.0       | Rev 0.5          | Base Specification              | Transmitter (Section 4.1.2)                                                     |

Refer to <a href="http://www.pcisig.com/specifications/pciexpress/">http://www.pcisig.com/specifications/pciexpress/</a> for the latest specifications.

<sup>&</sup>lt;sup>1</sup> **Disclaimer:** The tests provided in DPOJET (which are described in this document) do not guarantee PCI Express compliance. The test results should be considered "Pre-Compliance". Official PCI Express compliance and PCI-SIG Integrator List qualification is governed by the PCI-SIG (Special Interest Group) and can be achieved only through official PCI-SIG sanctioned testing.

In this document, for all references to the PCI Express Base Specifications and Card Electrical Mechanical (CEM) specifications, refer to all versions of the Spec. (Rev 1.1, 2.0, and 3.0). Differences between the specifications are specifically called out when appropriate.

In the subsequent sections, step-by-step procedures are described to help you perform PCI Express measurements. Each measurement is described as a Method of Implementation (MOI). For further reference, consult the Compliance checklists and tools offered to PCI-SIG members at <a href="https://www.pcisig.com">www.pcisig.com</a>.

# **2 PCI Express Specifications**

As shown in Table 1, Electrical Specifications for PCI Express are provided in multiple documents. This section provides a summary of the measurement parameters measured in the DPOJET Setup Library module and how they are related to the symbol and test limits in the specification.

## 2.1 Differential Transmitter (TX) Output Specifications

The following table shows the available measurements in the PCE Module and their test limits defined in each of the Base Specifications.

| Table 2- Supported B | ase Specification t | transmitter measurements | ; |

|----------------------|---------------------|--------------------------|---|

| . ab.o = Cappo.toa = | acc opcomounem      |                          | , |

|                                             |                                                   |                                                                         |                                                                                                       | Specification                                                                                                         |                                                                                    |

|---------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Parameter                                   | Symbol(s)                                         | DPOJET<br>Measurement                                                   | 2.5GT/s<br>Rev1.1/Rev2.0                                                                              | 5.0 GT/s<br>Rev2.0                                                                                                    | 8.0 GT/s<br>Rev3.0                                                                 |

| Clock Recovery                              | NA                                                | See Setup by Data Rate >>                                               | 1st Order PLL Fc: 1MHz Emulates 1st Order filter at 1.5MHz with 75% edge density of Compliance Pattem | 2nd Order PLL CDR w/ .707 Damping Fc: 1.0MHz - And - 3rd Order LPF Fc: 1.5MHz Emulates Step Function Filter at 1.5MHz | 1st Order PLL Fc: 10MHz Assumes Scrambled Compliance Pattern with 50% Edge Density |

| Unit interval                               | UI                                                | PCIe UI<br>(min/max)<br>SSC filtered with 3rd order<br>HPF: Fc = 198kHz | 399.98 (min)<br>400.12 (max)                                                                          | 199.94 (min)<br>200.06 (max)                                                                                          | 124.9625 (min)<br>125.0375 (max)                                                   |

| Differential p-p TX voltage swing           | $V_{TX-DIFFp-p}$ $V_{TX-SWING}$ $V_{TX-EYE-FULL}$ | PCle T-Tx-Diff-PP<br>Eye Height                                         | 0.8 V (min)<br>1.2 V (max)                                                                            | 0.8 V (min)<br>1.2 V (max)                                                                                            | TBD<br>1.2 V (max)                                                                 |

| Low power differential p-p TX voltage swing | VTX-SWING-LOW VTX-EYE-HALF                        | PCle T-Tx-Diff-PP<br>Eye Height                                         | Not Specified                                                                                         | 0.4 V (min)<br>0.7 V (max)                                                                                            | 0.1 V (min)<br>0.8 V (max)                                                         |

| De-emphasized output voltage ratio          | $V_{TX-DE-RATIO}$                                 | PCle T/nT Ratio                                                         | -3.0 dB (min)<br>-4.0 dB (max)                                                                        | -5.5 dB (min)<br>-6.5 dB (max)<br>or<br>-3.0 dB (min)<br>-4.0 dB (max)                                                | Not Specified                                                                      |

|                                                                              |                                          |                                                                              | Specification            |                    |                    |

|------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------|--------------------------|--------------------|--------------------|

| Parameter                                                                    | Symbol(s)                                | DPOJET<br>Measurement                                                        | 2.5GT/s<br>Rev1.1/Rev2.0 | 5.0 GT/s<br>Rev2.0 | 8.0 GT/s<br>Rev3.0 |

| Instantaneous lane                                                           | T <sub>MIN-PULSE</sub>                   | PCle Tmin-Pulse                                                              | Not Specified            | 0.9UI (min)        | Not Specified      |

| pulse width                                                                  |                                          |                                                                              |                          | 150 ps (min)       |                    |

| Transmitter eye                                                              | $T_{TX-EYE}$                             | For Rev1.1: Eye Width                                                        | .75 UI (min)             | .75 UI (min)       | TBD                |

| including all jitter sources                                                 | ttx-eye_tj                               | For Rev2/3: PCle T-TXA                                                       | 300 ps (min)             | 150 ps (min)       |                    |

| Maximum time between the jitter median and maximum deviation from the median | T <sub>TX-EYEMEDIAN-to</sub> - MAXJITTER | PCle Med-Mx Jitter                                                           | .125 UI<br>(min/max)     | Not Specified      | Not Specified      |

| Deterministic jitter                                                         | $T_{TX	ext{-}DJ	ext{-}DD}$               | DJ–δδ                                                                        | Not Specified            | 0.15 UI (max)      | TBD                |

|                                                                              |                                          |                                                                              |                          | 30 ps (max)        |                    |

| Tx RMS jitter < 1.5MHz                                                       | Ttx-lf-rms                               | TIE1 Jitter w/<br>3 <sup>rd</sup> Order LPF<br>Fc: 1.5 MHz<br>Std. Deviation | Not Specified            | 3.0 ps (max)       | Not Specified      |

| D+/D- TX output rise/fall                                                    | $T_{TX-RISE}$                            | PCIe T-Tx-Rise                                                               | 0.125 UI (min)           | 0.15 UI (min)      | Not Specified      |

| Time <sup>2</sup>                                                            | $T_{TX-FALL}$                            | PCIe T-Tx-Fall                                                               | 50 ps (min)              | 30 ps (min)        |                    |

| Tx rise/fall<br>mismatch                                                     | Trf-mismatch                             | PCle T-RF-Mismch                                                             | Not Specified            | 0.1 UI (max)       | Not Specified      |

| AC common mode output voltage                                                | V <sub>TX-CM-AC-PP</sub>                 | Common Mode<br>Pk-Pk                                                         | Not Specified            | 100 mV (max)       | 100 mV (max)       |

| AC common mode                                                               | V <sub>TX-CM-AC-P</sub>                  | Common Mode                                                                  | 20mV RMS                 | Not Specified      | 20mV RMS           |

| output voltage                                                               |                                          | Rev1.1 : StdDev                                                              | (max)                    |                    | (max)              |

| Absolute delta of DC                                                         | $V_{TX-CM-DC-LINE-DELTA}$                | Common Mode                                                                  | 0 V (min)                | 0 V (min)          | 0 V (min)          |

| common mode voltage between D+ and D-                                        |                                          | Mean                                                                         | 25 mV (max)              | 25 mV (max)        | 25 mV (max)        |

$<sup>^2</sup>$  Rise/Fall time measurements in DPOJET are compliant to the Rev1.0a and Rev1.1 specification. For Gen2, rise and fall time is limited to TF2 and TR2 as defined in section 4.3.3.8 of the Base Specification

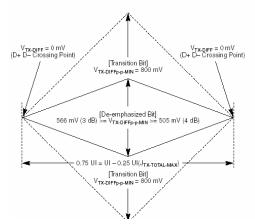

### Differential Transmitter (TX) Compliance Eye Diagrams

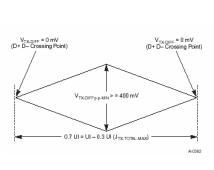

Figure 1a shows the eye mask definitions for the Rev1.1 Base specification. It provides an example of a transmitter mask for a signal with de-emphasis. Transition and non-transition bits must be separated to perform the mask testing. The amplitude and jitter mask geometries are derived from the amplitude and jitter specifications. Low power transmitter variants in both Gen1 and Gen2 do not use de-emphasis (This is shown in Figure 1b).

Rev1.1/2.0 Transmitter eye masks for transition and non-transition bits

Rev1.1/2.0 transmitter eye mask for low power variant where deemphasis is not used

Rev3.0 transmitter eye mask definition – Mask Geometries TBD for Gen3.

Figure 1: PCI Express Transmitter Eye Mask Definitions

# 2.2 Differential Receiver (RX) Input Specifications

The following table shows the available measurements in the PCE Module and their test limits defined in each of the Base specifications.

Table 3 – Supported base specification receiver measurements

|                                                      |                               | DPOJET                                                 | 2.5GT/s                                                            | 5.0 GT/s                                            | 8.0 GT/s                               |

|------------------------------------------------------|-------------------------------|--------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------|

| Parameter                                            | Symbol                        | Measurement                                            | Rev1.1/Rev2.0                                                      | Rev2.0                                              | Rev3.0                                 |

| Clock Recovery                                       | NA                            | See Setup by Data Rate >>                              | 1 <sup>st</sup> Order PLL<br>Fc: 1MHz                              | 2 <sup>nd</sup> Order PLL<br>CDR w/ .707<br>Damping | 1 <sup>st</sup> Order PLL<br>Fc: 10MHz |

|                                                      |                               |                                                        |                                                                    | Fc: 1.0MHz                                          |                                        |

|                                                      |                               |                                                        |                                                                    | - And -<br>3 <sup>rd</sup> Order LPF                | Assumes                                |

|                                                      |                               |                                                        | Emulates 1st Order                                                 | Fc: 1.5MHz                                          | Scrambled<br>Compliance                |

|                                                      |                               |                                                        | filter at 1.5MHz with<br>75% edge density of<br>Compliance Pattern | Emulates Step<br>Function Filter at<br>1.5MHz       | Pattern with<br>50% Edge<br>Density    |

| Unit interval                                        | UI                            | PCIe UI                                                | 399.98 (min)                                                       | 199.94 (min)                                        | 124.9625 (min)                         |

|                                                      |                               | (min/max) SSC filtered with 3rd order HPF: Fc = 198kHz | 400.12 (max)                                                       | 200.06 (max)                                        | 125.0375 (max)                         |

| Minimum receiver eye height                          | $V_{RX\_EYE}$                 | PCle T-Tx-Diff-PP                                      | .175 V (min)                                                       | .120 V (min)                                        | .120 V (min)                           |

|                                                      |                               | Eye Height                                             | 1.2 V (max)                                                        | 1.2 V (max)                                         | 1.2 V (max)                            |

| Minimum receiver eye width                           | $T_{RX-EYE}$                  | For Rev1.1: Eye Width                                  | .40 UI (min)                                                       | .40 UI (min)                                        | TBD                                    |

|                                                      | IXI BIE                       | For Rev2/3: Width@BER                                  | 160ps (min)                                                        | 80ps (min)                                          |                                        |

| Receiver deterministic jitter –                      | $T_{RX\_DJ\_DD}$              | DJ–δδ                                                  | Not Specified                                                      | .44 UI (max)                                        | TBD                                    |

| Dj                                                   |                               |                                                        |                                                                    | 88ps (max)                                          |                                        |

| Minimum width                                        | Trx-min-pulse                 | PCIe Tmin-Pulse                                        | Not Specified                                                      | .60 UI (min)                                        | Not Specified                          |

| pulse at Rx                                          |                               |                                                        |                                                                    | 120ps (max)                                         |                                        |

| Maximum time between the                             | T <sub>TX-EYEMEDIAN-to-</sub> | PCIe Med-Mx Jitter                                     | .30 UI (max)                                                       | Not                                                 | Not                                    |

| jitter median and maximum deviation from the median. | MAXJITTER                     |                                                        |                                                                    | Specified                                           | Specified                              |

| Rx AC common                                         | VRX-CM-AC-P                   | Common Mode                                            | 150mV                                                              | 150mV                                               | Not Spedified                          |

| mode voltage                                         |                               | Rev2/3 : Pk-Pk                                         |                                                                    |                                                     |                                        |

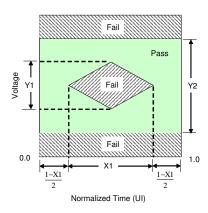

## Differential Receiver (RX) Eye Diagrams

Figure 2 shows the receiver eye mask definitions for the Rev1.1 Base specification. The amplitude and jitter mask geometries are derived from the amplitude and jitter specifications.

Figure 2: Receiver input eye mask

# 2.3 Add-In Card Transmitter Path Compliance Specifications

Table 4 is derived from the Electrical Mechanical Specifications (CEM). See the CEM Specification for additional notes and test definitions.

Table 4 - Supported CEM add-in card measurements

| Parameter                                                          | Symbol                                    | DPOJET                                          | 2.5GT/s                               | 5.0 GT/s                                            | 8.0 GT/s |

|--------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------|---------------------------------------|-----------------------------------------------------|----------|

|                                                                    |                                           | Measurement                                     | Rev1.1/Rev2.0                         | Rev2.0                                              | Rev3.0   |

| Clock Recovery                                                     | NA                                        | See Setup by Data Rate >>                       | 1 <sup>st</sup> Order PLL<br>Fc: 1MHz | 2 <sup>nd</sup> Order PLL<br>CDR w/ .707<br>Damping | TBD      |

|                                                                    |                                           |                                                 |                                       | Fc: 1.0MHz                                          |          |

|                                                                    |                                           |                                                 | Emulates 1st                          | - And -                                             |          |

|                                                                    |                                           |                                                 | Order filter at                       | 3 <sup>rd</sup> Order LPF                           |          |

|                                                                    |                                           |                                                 | 1.5MHz with 75% edge density of       | Fc: 1.5MHz                                          |          |

|                                                                    |                                           |                                                 | Compliance<br>Pattern                 | Emulates Step<br>Function Filter at<br>1.5MHz       |          |

| Unit interval                                                      | UI                                        | PCle UI                                         | 399.98 (min)                          | 199.94 (min)                                        | TBD      |

|                                                                    |                                           | (min/max)                                       | 400.12 (max)                          | 200.06 (max)                                        |          |

|                                                                    |                                           | SSC filtered with 3rd order<br>HPF: Fc = 198kHz |                                       |                                                     |          |

| Eye height of transition                                           | $V_{TXA}$                                 | Eye Height1                                     | .514 V (min)                          | 3.5dB De-emphasis                                   | TBD      |

| bits                                                               |                                           |                                                 | 1.2 V (max)                           | .380 V (min)                                        |          |

|                                                                    |                                           |                                                 |                                       | 1.2 V (max)                                         |          |

|                                                                    |                                           |                                                 |                                       | 6.0dB De-emphasis<br>.306 V (min)                   |          |

|                                                                    |                                           |                                                 |                                       | 1.2 V (max)                                         |          |

| Eye height of non-                                                 | $V_{TXA\_d}$                              | Eye Height2                                     | .360 V (min)                          | 3.5dB De-emphasis                                   | TBD      |

| transition bits                                                    |                                           |                                                 |                                       | .380 V (min)                                        |          |

|                                                                    |                                           |                                                 |                                       | 1.2 V (max)                                         |          |

|                                                                    |                                           |                                                 |                                       | 6.0dB De-emphasis<br>.260 V (min)                   |          |

|                                                                    |                                           |                                                 |                                       | 1.2 V (max)                                         |          |

| Eye width with sample size of 10 <sup>6</sup> UI                   | T <sub>TXA</sub> In Rev1.1                | Eye Width                                       | 287 ps (min)                          | Not Specified                                       | TBD      |

| Jitter eye opening at                                              | T <sub>TXA</sub> In Rev2.0                | For Rev1.1: Eye Width                           | 274 ps (min)                          | 123 ps (min)                                        | TBD      |

| BER 10 <sup>-12</sup>                                              |                                           | For Rev2/3: PCIe T-TXA                          | Informative                           | with Crosstalk                                      |          |

| Maximum median-max<br>jitter outlier with sample<br>size of 106 UI | J <sub>TXA-MEDIAN-to-</sub><br>MAX-JITTER | PCIe Med-Mx Jitter                              | 56.5 ps (max)                         | Not Specified                                       | TBD      |

| Total Jitter at BER 10-12                                          | Tj at BER 10 <sup>-12</sup>               | TJ@BER                                          | Not Specified                         | 77 ps (max)                                         | TBD      |

| Deterministic Jitter at BER 10-12                                  | Max Dj                                    | DJ–δδ                                           | Not Specified                         | 57 ps (max)                                         | TBD      |

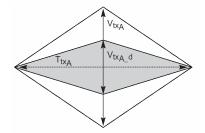

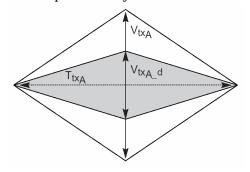

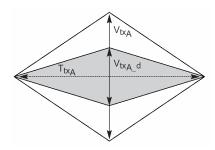

## **Add-In Card Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 4.

Figure 3: Add-in card compliance eye masks

# 2.4 System Board Transmitter Path Specifications

Table 5 is derived from the Electrical Mechanical Specifications (CEM). See the CEM Specification for additional notes and test definitions.

Table 5 – Supported CEM System Board Measurements

| Parameter                                                                | Symbol                                         | DPOJET                                                       | 2.5GT/s                                              | 5.0 GT/s                                                           | 8.0 GT/s |

|--------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|----------|

|                                                                          |                                                | Measurement                                                  | Rev1.1/Rev2.0                                        | Rev2.0                                                             | Rev3.0   |

| Clock Recovery                                                           | NA                                             | See Setup by Data Rate >>                                    | 2 <sup>nd</sup> Order PLL<br>CDR w/ .707<br>Damping  | Explicit Clock 2 <sup>nd</sup><br>Order PLL<br>Clock Multiplier=50 | TBD      |

|                                                                          |                                                |                                                              | Fc: 1.0MHz<br>- And -                                | CDR w/ .707<br>Damping                                             |          |

|                                                                          |                                                |                                                              | 1 <sup>st</sup> Order LPF                            | Fc: 1.0MHz                                                         |          |

|                                                                          |                                                |                                                              | Fc: 1.5MHz                                           |                                                                    |          |

|                                                                          |                                                |                                                              | Emulates 3 <sup>rd</sup><br>Order 3500:250<br>Method | Emulates Step<br>Function Filter at<br>1.5MHz                      |          |

| Unit interval                                                            | UI                                             | PCle UI                                                      | 399.98 (min)                                         | 199.94 (min)                                                       | TBD      |

|                                                                          |                                                | (min/max)<br>SSC filtered with 3rd order<br>HPF: Fc = 198kHz | 400.12 (max)                                         | 200.06 (max)                                                       |          |

| Eye height of transition bits                                            | V <sub>TXS</sub>                               | . Eye Height1                                                | .274 V (min)                                         | .250 V (min)                                                       | .TBD     |

|                                                                          |                                                |                                                              | 1.2 V (max)                                          | 1.2 V (max)                                                        |          |

| Eye height of non-transition bits                                        | $V_{TXS\_d}$                                   | Eye Height2                                                  | .253 V (min)                                         | .250 V (min)                                                       | TBD      |

| Eye width with sample size of                                            | T <sub>TXS</sub>                               | Eye Width                                                    | 246 ps (min)                                         | Not Specified                                                      | TBD      |

| 10 <sup>6</sup> UI                                                       | In Rev1.1                                      |                                                              |                                                      |                                                                    |          |

| Jitter eye opening at BER 10 <sup>-12</sup>                              | $T_{TXS}$                                      | For Rev1.1: Eye Width                                        | 233 ps (min)                                         | 95 ps (min)                                                        | TBD      |

|                                                                          | In Rev2.0                                      | For Rev2/3: PCIe T-TXA                                       | Informative                                          | with Crosstalk                                                     |          |

| Maximum median-max jitter outlier with sample size of 10 <sup>6</sup> UI | J <sub>TXA</sub> -<br>MEDIAN-to-<br>MAX-JITTER | PCIe Med-Mx Jitter                                           | 77 ps (max)                                          | Not Specified                                                      | TBD      |

| Total Jitter at BER 10 <sup>-12</sup>                                    | Tj at BER<br>10 <sup>-12</sup>                 | TJ@BER                                                       | Not Specified                                        | 77 ps (max)                                                        | TBD      |

| Deterministic Jitter at BER 10 <sup>-12</sup>                            | Max Dj                                         | DJ–δδ                                                        | Not Specified                                        | 57 ps (max)                                                        | TBD      |

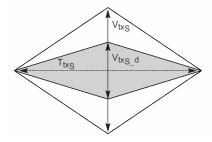

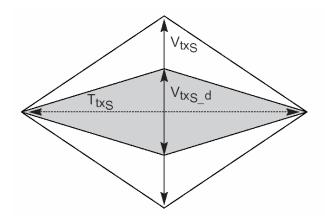

# **System Board Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 5.

Figure 4: System Board Compliance Eye Masks

# 2.5 PCI ExpressModule™ Specifications

The specifications in this section are taken from the PCI Express ExpressModule<sup>TM</sup> specification, which is a companion specification to the *PCI Express Base specification*. Its primary focus is the implementation of a modular I/O form factor that is focused on the needs of workstations and servers. Measurements in the PCE module support add-in card and system transmitter path measurements at the PCI Express connector.

### **ExpressModule Add-In Card Transmitter Path Specifications**

Table 6 is derived from Section 5.4.1 of the ExpressModule Electro-Mechanical Specifications Rev. 1.0.

Table 6 - Supported ExpressModule Add-In Card Measurements

| Parameter                                                                | Symbol                                    | DPOJET                                                         | Rev1.0                                                                                                |

|--------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                                                          |                                           | Measurement                                                    |                                                                                                       |

| Clock Recovery                                                           | NA                                        | See Setup by<br>Data Rate >>                                   | 1st Order PLL Fc: 1MHz Emulates 1st Order filter at 1.5MHz with 75% edge density of Compliance Pattem |

| Unit interval                                                            | UI                                        | PCIe UI (min/max) SSC filtered with 3rd order HPF: Fc = 198kHz | 399.98 (min)<br>400.12 (max)                                                                          |

| Eye height of transition Bits                                            | V <sub>TXA</sub>                          | . Eye Height1                                                  | .514 V (min)<br>1.2 V (max)                                                                           |

| Eye height of non-transition Bits                                        | $V_{TXA\_d}$                              | Eye Height2                                                    | .360 V (min)                                                                                          |

| Eye width with sample size of 10 <sup>6</sup> UI                         | T <sub>TXA</sub><br>In Rev1.1             | Eye Width                                                      | 287 ps (min)                                                                                          |

| Jitter eye opening at BER 10 <sup>-12</sup>                              |                                           | Eye<br>Width@BER                                               | 274 ps (min)<br>Informative                                                                           |

| Maximum median-max jitter outlier with sample size of 10 <sup>6</sup> UI | J <sub>TXA-MEDIAN-to-</sub><br>MAX-JITTER | PCIe Med-Mx<br>Jitter                                          | 56.5 ps (max)                                                                                         |

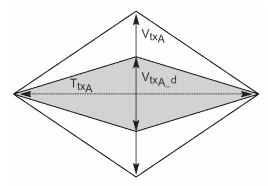

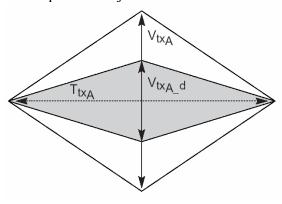

# **ExpressModule Add-In Card Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 6.

Figure 5: ExpressModule add-in card compliance eye masks

# **ExpressModule System Board Transmitter Path Specifications**

Table 7 is derived from Section 5.4.3 of the ExpressModule Electro-Mechanical Specifications Rev. 1.0.

Table 7 – Supported ExpressModule system board measurements

| Parameter                                                    | Symbol                                    | DPOJET                                                                     | Gen1                                                                                                                                                                      |

|--------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                              |                                           | Measurement                                                                | Rev1.0                                                                                                                                                                    |

| Clock Recovery                                               | NA                                        | See Setup by Data<br>Rate >>                                               | 2 <sup>nd</sup> Order PLL CDR w/ .707 Damping<br>Fc: 1.0MHz<br>- And -<br>1 <sup>st</sup> Order LPF<br>Fc: 1.5MHz<br><i>Emulates 3<sup>rd</sup> Order 3500:250 Method</i> |

| Unit interval                                                | UI                                        | PCIe UI<br>(min/max)<br>SSC filtered with 3rd<br>order HPF: Fc =<br>198kHz | 399.98 (min)<br>400.12 (max)                                                                                                                                              |

| Eye height of transition bits                                | V <sub>TXS</sub>                          | . Eye Height1                                                              | .274 V (min)                                                                                                                                                              |

|                                                              |                                           |                                                                            | 1.2 V (max)                                                                                                                                                               |

| Eye height of non-transition bits                            | $V_{TXS\_d}$                              | Eye Height2                                                                | .253 V (min)                                                                                                                                                              |

| Eye width with sample size of 10 <sup>6</sup> UI             | T <sub>TXS</sub>                          | Eye Width                                                                  | 246 ps (min)                                                                                                                                                              |

| Jitter eye opening at BER 10 <sup>-12</sup>                  |                                           | Eye Width@BER                                                              | 233 ps (min)                                                                                                                                                              |

| Maximum median-max jitter outlier with sample size of 106 UI | J <sub>TXA-MEDIAN-</sub><br>to-MAX-JITTER | TIE Jitter                                                                 | 77 ps (max)                                                                                                                                                               |

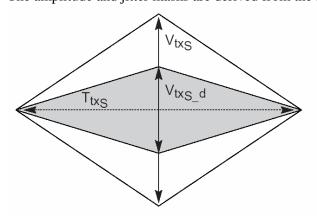

# **Express Module System Board Compliance Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table6.

Figure 6: ExpressModule system board compliance eye masks

### 2.6 PCI Express External Cabling Specifications

The specifications in this section are taken from the PCI Express External Cabling Specification. Its primary focus is the implementation of a cabled interconnect. Measurements in the PCE module support transmitter path and receiver path measurements. These measurements represent the test points at the transmitter end of the cable and the receiver end of the cable respectively.

## **External Cabling Transmitter Path Specifications**

Table 8 is derived from Section 3.3.1 of the External Cabling Specification Rev. 1.0.

Table 8 - Supported external cabling transmitter path measurements

| Parameter                                   | Symbol                                     | DPOJET<br>Measurement                                                      | Rev1.0                                                                                                 |

|---------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Clock Recovery                              | NA                                         | See Setup by Data<br>Rate >>                                               | 1st Order PLL Fc: 1MHz Emulates 1st Order filter at 1.5MHz with 75% edge density of Compliance Pattern |

| Unit interval                               | UI                                         | PCIe UI<br>(min/max)<br>SSC filtered with 3rd<br>order HPF: Fc =<br>198kHz | 399.98 (min)<br>400.12 (max)                                                                           |

| Eye height of transition bits               | V <sub>TXA</sub>                           | . Eye Height1                                                              | .654 V (min)<br>1.2 V (max)                                                                            |

| Eye height of non-transition bits           | $V_{TXA\_d}$                               | Eye Height2                                                                | .450 V (min)                                                                                           |

| Jitter eye opening at BER 10 <sup>-12</sup> | Trxa@ BER 10 <sup>-12</sup>                | Eye Width@BER                                                              | 296 ps (min)                                                                                           |

| Eye width with sample size of 106 UI        | Trx <sub>A</sub> @ 10 <sup>6</sup> Samples | Eye Width                                                                  | 309 ps (min)                                                                                           |

### **Cable (Transmitter Side) Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications.

Figure 7: Cable (transmitter side) compliance eye masks

# **External Cabling Receiver Path Specifications**

Table 9 is derived from Section 3.3.2 of the External Cabling Specification Rev. 1.0.

Table 9 – Supported CEM system board measurements

| Parameter                                   | Symbol                        | DPOJET                                                                     | Gen1                                                                                        |

|---------------------------------------------|-------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                                             |                               | Measurement                                                                | Rev1.0                                                                                      |

| Clock Recovery                              | NA                            | See Setup by Data<br>Rate >>                                               | 1 <sup>st</sup> Order PLL<br>Fc: 1MHz                                                       |

|                                             |                               |                                                                            | Emulates 1st Order<br>filter at 1.5MHz with<br>75% edge density<br>of Compliance<br>Pattern |

| Unit interval                               | UI                            | PCIe UI<br>(min/max)<br>SSC filtered with<br>3rd order HPF: Fc =<br>198kHz | 399.98 (min)<br>400.12 (max)                                                                |

| Eye height of transition bits               | V <sub>RXA</sub>              | . Eye Height1                                                              | .208 V (min)                                                                                |

|                                             |                               |                                                                            | 1.2 V (max)                                                                                 |

| Eye height of non-transition bits           | $V_{RXA\_d}$                  | Eye Height2                                                                | .192 V (min)                                                                                |

| Jitter eye opening at BER 10 <sup>-12</sup> | Trxa@ BER 10 <sup>-12</sup>   | Eye Width@BER                                                              | 234 ps (min)                                                                                |

| Eye width with sample size of 106 UI        | Trxa@ 10 <sup>6</sup> Samples | Eye Width                                                                  | 247 ps (min)                                                                                |

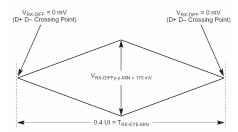

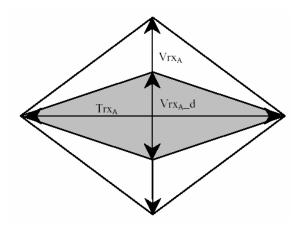

# Cable (Receive Side) Eye Diagrams

The amplitude and jitter masks are derived from the amplitude and jitter specifications.

Figure 8: Cable (receiver side) compliance eye masks

### 2.7 PCMCIA ExpressCard™ Specifications

The specifications in this section are taken from the PCMCIA ExpressCard Standard (Release 1.0). Its primary focus is a small modular add-in card technology based on PCI Express and USB interfaces. Measurements in the PCE module support host system and ExpressCard transmitter path measurements.

### **ExpressCard - Module Transmitter Path Specifications**

Table 10 is derived from Section 4.2.1.3.2 of the ExpressCard Specification Release 1.0.

| Table 10 - Supported | EvnraceCard   | transmitter nat  | n mascuramante      |

|----------------------|---------------|------------------|---------------------|

| Table 10 – Subbolled | i Expressuaru | transmitter bati | i illeasureilleilis |

| Parameter                         | Symbol           | DPOJET                                                                     | Release 1.0                                                                                            |

|-----------------------------------|------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|                                   |                  | Measurement                                                                |                                                                                                        |

| Clock Recovery                    | NA               | See Setup by Data<br>Rate >>                                               | 1st Order PLL Fc: 1MHz Emulates 1st Order filter at 1.5MHz with 75% edge density of Compliance Pattern |

| Unit interval                     | UI               | PCIe UI<br>(min/max)<br>SSC filtered with 3rd<br>order HPF: Fc =<br>198kHz | 399.98 (min)<br>400.12 (max)                                                                           |

| Eye height of transition bits     | $V_{TXA}$        | . Eye Height1                                                              | 538 V (min)<br>1.2 V (max)                                                                             |

| Eye height of non-transition bits | $V_{TXA\_d}$     | Eye Height2                                                                | .368 V (min)                                                                                           |

| Eye width across any 250 UIs      | T <sub>TXA</sub> | Eye Width@BER                                                              | 237 ps (min)                                                                                           |

### **ExpressCard Transmitter Path Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 10.

Figure 9: ExpressCard Module Transmitter compliance eye masks

# **ExpressCard - Host System Transmitter Path Specifications**

Table 11 from Section 4.2.1.3.2 of the ExpressCard Specification Release 1.0.

Table 11 - Supported ExpressCard Host System Transmitter Path Measurements

| Parameter                         | Symbol       | DPOJET                       | Release 1.0                                                                                                          |

|-----------------------------------|--------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                   |              | Measurement                  |                                                                                                                      |

| Clock Recovery                    | NA           | See Setup by Data<br>Rate >> | 2 <sup>nd</sup> Order PLL CDR w/<br>.707 Damping<br>Fc: 1.0MHz<br>- And -<br>1 <sup>st</sup> Order LPF<br>Fc: 1.5MHz |

|                                   |              |                              | Emulates 3 <sup>rd</sup> Order<br>3500:250 Method                                                                    |

| Unit interval                     | UI           | PCIe UI<br>(min/max)         | 399.98 (min)                                                                                                         |

|                                   |              | SSC filtered with 3rd        | 400.12 (max)                                                                                                         |

|                                   |              | order HPF: Fc =<br>198kHz    |                                                                                                                      |

| Eye height of transition bits     | $V_{txS}$    | . Eye Height1                | .262 V (min)                                                                                                         |

|                                   |              |                              | 1.2 V (max)                                                                                                          |

| Eye height of non-transition bits | $V_{txS\_d}$ | Eye Height2                  | .247 V (min)                                                                                                         |

| Eye width across any 250 Uls      | $T_{TxS}$    | Eye Width@BER                | 183 ps (min)                                                                                                         |

# **ExpressCard – Host System Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 11.

Figure 10: ExpressCard Host System compliance eye masks

# **3 PCI Express Library Contents**

The following table shows a list of the PCI Express standards supported by the DPOJET Setup Library and their default probing configurations. The Setup File Library is located in C:\TekApplications\DPOJET\PCIE\Setups

Table 12 – Setup Files and default probing configurations

| •                                    | Table 12 – Setup Files and detault probing configurations |                                 |                                     |  |  |

|--------------------------------------|-----------------------------------------------------------|---------------------------------|-------------------------------------|--|--|

| PCI-SIG Specification                | Bit Rate                                                  | Setup File Name                 | Default Probing<br>Configuration    |  |  |

| Rev1.1 Base Specification            | 2.5GT/s                                                   | Rev11_Tx_Base.set               | Data = Math1 - Ch1-Ch2              |  |  |

| Transmitter and Receiver             |                                                           | Rev11_Rx_Base.set               |                                     |  |  |

| Rev1.1 CEM Specification             | 2.5GT/s                                                   | Rev11_Tx_ADD_CON.set            | Data = Math1 - Ch1-Ch2              |  |  |

| Add-In Card and System               |                                                           | Rev11_Tx_SYSTEM.set             |                                     |  |  |

| Rev1.0 Cable                         | 2.5GT/s                                                   | Rev10_Tx_Cable.set              | Data = Math1 - Ch1-Ch2              |  |  |

| Specification                        |                                                           | Rev10_Rx_Cable.set              |                                     |  |  |

| Near End and Far End                 |                                                           |                                 |                                     |  |  |

| Rev1.0 ExpressModule                 | 2.5GT/s                                                   | Rev10_Tx_ExpMod_ADD_CON.set     | Data = Math1 - Ch1-Ch2              |  |  |

| Specification                        |                                                           | Rev10_Tx_ExpMod_SYSTEM.set      |                                     |  |  |

| Add-In Card and System               |                                                           |                                 |                                     |  |  |

| Rev1.0 ExpressCard                   | 2.5GT/s                                                   | Rev10_Tx_ExpressCard_Host.set   | Data = Math1 - Ch1-Ch2              |  |  |

| Specification                        |                                                           | Rev10_Tx_ExpressCard_Module.set |                                     |  |  |

| Host and Module                      |                                                           |                                 |                                     |  |  |

| Rev2.0 Base Specification            | 5GT/s                                                     | Rev20_Base_Tx_3.5dB.set         | Data = Math1 - Ch1-Ch2              |  |  |

| Transmitter with 3.5dB               |                                                           | Rev20_Base_Tx_6.0dB.set         |                                     |  |  |

| and 6.0 dB De-Emphasis and Low Swing |                                                           | Rev20_Base_Tx_Low_Swing.set     |                                     |  |  |

| Rev2.0 CEM Specification             | 5GT/s                                                     | Rev20_Tx_ADD_CON_3.5dB.set      | Add-In Card:                        |  |  |

| Add-In Card with 3.5dB               |                                                           | Rev20_Tx_ADD_CON_6.0dB.set      | Data = Math1 - Ch1-Ch2              |  |  |

| and 6.0dB De-Emphasis and System     |                                                           | Rev20_Tx_SYSTEM.set             | System:<br>RefClk = Math1 = Ch1-Ch2 |  |  |

| and System                           |                                                           |                                 | Data = Math2 = Ch3 - Ch4            |  |  |

| Rev 3.0 Base Specification           | 8GT/s                                                     | Rev30_Base_Tx.set               | Data = Math1 – Ch1-Ch2              |  |  |

| (Draft)                              |                                                           | Rev30_Base_Tx_Half_Swing.set    |                                     |  |  |

| Transmitter Full and Half<br>Swing   |                                                           | -                               |                                     |  |  |

To change the probing configuration to use differential probes, change the Source of the Data and RefClk as appropriate in the measurement configuration menu in DPOJET. Refer to the DPOJET OLH (Online Help) for details.

# **4 Preparing to Take Measurements**

## 4.1 Required Equipment

The following equipment is required to take the measurements:

- Oscilloscope Selection:

- Rev 1.1 (2.5 GT/s) The PCI-SIG recommends a minimum of 6 GHz system BW for compliance testing. However, some silicon can have rise times in the 50ps range. Thus, Tektronix recommends DPO/DSA70000 8GHz and above for 2.5GT/s transmitter measurements.

- o Rev 2.0 (5 GT/s) DPO/DSA70000 12.5 GHz and above are recommended for 5GT/s and above and required for Base Specification transmitter measurements.

- Rev 3.0 (8 GT/s) DPO/DSA70000 16 GHz and above are recommended for 8GT/s measurements.

- DPOJET software (Version 2.1 or above) with PCI Express Measurements (Opt. PCE) installed.

- Probes See Section 3.2 for probing options.

- Test Fixtures

- Test Fixtures for System and Add-In card testing are available from the PCI-SIG. Rev1.1 Fixtures (CLB1, CBB1) break transmitter signals out into SMA connections. Rev 2.0 Fixtures (CLB2, CBB2) break transmitter signals out into SMP connections. These fixtures are available at:

- http://www.pcisig.com/specifications/ordering\_information/ordering\_information.

- Test fixtures for ExpressCard testing are available from the following URL: <a href="http://www.expresscard.org/web/site/testtools.jsp">http://www.expresscard.org/web/site/testtools.jsp</a>

### 4.2 Probing Options for Transmitter Testing

The first step is to probe the link. Use one of the following four methods to connect probes to the link.

### **SMA Input Connection**

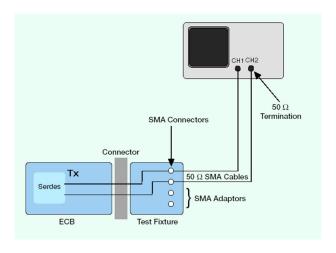

# A. Two TCA-SMA inputs using SMA cables (Ch1) and (Ch2)

The differential signal is created from the math waveform (Math1 = Ch1-Ch2). The Common mode AC measurement is also available in this configuration from the common mode waveform (Ch1+Ch3)/2. This probing technique requires breaking the link and terminating into a 50  $\Omega$ /side termination of the oscilloscope. While in this mode, the PCI Express SerDes will transmit the compliance test pattern. Ch-Ch de-skew is required using this technique because two channels are used. This configuration does not compensate for cable loss in the SMA cables. The measurement reference plane is at the input of the TCA-SMA connectors on the oscilloscope.

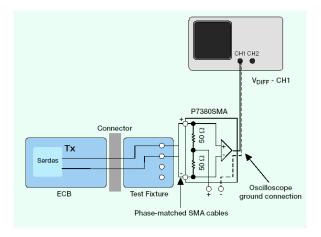

# **B.** One P7300SMA series differential active probe (Ch1)

The differential signal is measured across the termination resistors inside the P7300SMA series probe. This probing technique requires breaking the link. While in this mode, the PCI Express SerDes will transmit the compliance test pattern. Matched cables are provided with the probe to avoid introducing deskew into the system. Only one channel of the oscilloscope is used. The P7300SMA provides a calibrated system at the Test Fixture attachment point, eliminating the need to compensate for cable loss associated with the probe configuration A.

**SMA Pseudo-differential**

**SMA Input Differential Probe**

### **ECB** pad connection

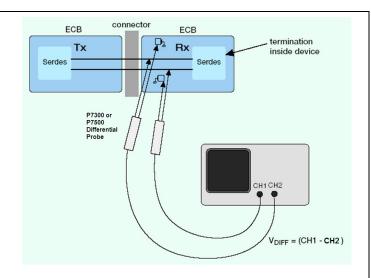

# C. Two active probes (Ch1) and (Ch2)

The differential signal is created from the math waveform (Math1 = Ch1-Ch2). The Common mode AC/DC measurements are available in this configuration from the common mode waveform (Ch1+Ch3)/2. This probing technique can be used for either a live link that is transmitting data, or a link that has terminated into a "dummy load." In both cases, the singleended signals should be probed as close as possible to the termination resistors on both sides with the shortest ground connection possible. Ch-Ch deskew is required using this technique because two channels are used.

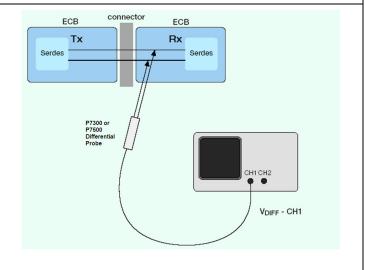

#### D. One P7300 or P7500 series Differential probe (Ch1)

The differential signal is measured directly across the termination resistors. This probing technique can be used for either a live link that is transmitting data, or a link that is terminated into a "dummy load." In both cases, the signals should be probed as close as possible to the termination resistors. De-skew is not necessary because a single channel of the oscilloscope is used. If using a P7500 Tri-Mode Probe, common mode voltage measurements can be made directly with the probe.

### **Dual Port Connection**

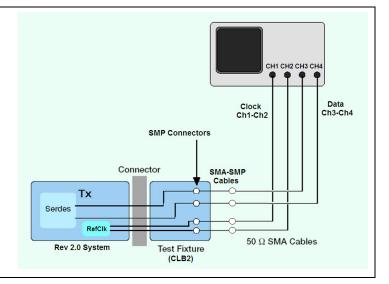

#### E. Dual Port

For Rev 2.0 System testing (Described in Section 2.4), the 'Dual Port' method is used to capture differential Data and RefClk. Direct SMA input can be used (where RefClk=Math1=Ch1-Ch2 and Data=Math2=Ch3-Ch4); or Two P7313SMA probes can be used (where RefClk = Ch1 and Data = Ch2).

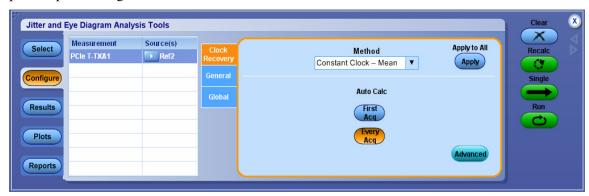

## 4.3 Running the Test

The following is a step-by-step procedure on how to run a test in the DPOJET PCI Express Setup Library. Refer to Table 12 for default probing configurations for each Setup.

From the DPO/DSA Analysis Menu, Select PCI Express. Allow DPOJET to load.

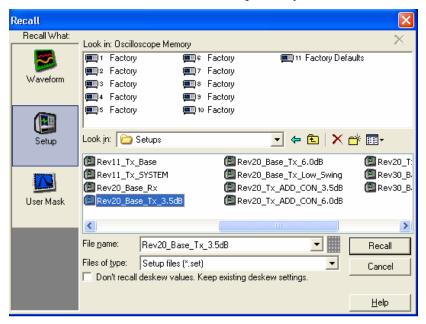

1. From the File Menu, Select Recall Setup and navigate to the DPOJET PCIE Setup Library

2. Recall the desired file from the Setup Library

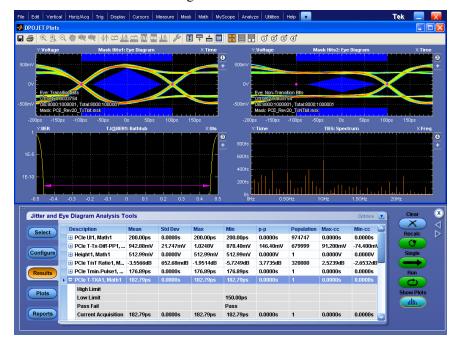

3. Press the 'Single' button on the instrument front panel. The screen should look similar to the following image. Adjust Vertical Scale to take full advantage of the A/D range of the oscilloscope enter channel De-Skew values as needed. The Horizontal Scale is set to capture 1 Million UI (10<sup>6</sup> bits) as required by the specifications.

4. Press the Single Button in DPOJET (Jitter and Eye Analysis Tools) Menu. The end result should look similar to the following screenshot. Pass/Fail results are viewed by expanding the measurement results using the '+' icon next to each measurement.

# 5 Parameter Definitions and Method of implementation

The DPOJET PCI Express Setup Library combines measurements native to the standard DPOJET package with with unique measurements offered in the **Standards** >> **PCI Express 2.0** tab of the DPOJET Measurement Select menu. PCI Express specific measurements require Opt. PCE is enabled and Version 2.1 or above of DPOJET is installed on the oscilloscope.

Measurements selected in the setup file are dependent on the specification that is designed to test. Refer to Table 2 thru Table 11 for the clock recovery method and measurements for each measurement in the setup file. Refer to the DPOJET OLH (Online Help) for measurement algorithms and setup parameters for measurements native to DPOJET.

The algorithm and setup parameters of the PCI Express specific measurements are described in the following sections.

### 5.1 UI (Unit Interval) MOI

#### **Definition:**

UI (Unit Interval) is defined in the base specification Rev2.0. This measurement is done using the PCIe–UI. The Result panel would display the Unit interval values

#### **Test Definition Notes from the Specification:**

The specified UI is equivalent to a tolerance of  $\pm 300$  ppm for each Refclk source. Period does not account for SSC induced variations.

#### **Limits:**

Refer to Table 2 thru Table 11 for specified limits on the UI measurement.

#### **Test Procedure:**

Ensure that *PCIe UI* is selected in the **Jitter and Eye diagram Analysis Tools >> Select** menu.

Set the following parameters

**Horizontal Record** length to at least 500K.

Configure >> Edges >> Auto

Configure >> Filter >> Low pass - 198kHz

**Configure >> Global >> off**

#### **Measurement Algorithm:**

The Unit interval measurement calculates the duration of a cycle as defined by a start and a stop edge. Edges are defined by polarity, threshold, and hysteresis. The application calculates clock period measurement using the following equation:

$$P_n^{Clock} = T_{n+1} - T_n$$

Where:

$P^{Clock}$  is the clock period.

*T* is the VRefMid crossing time for the selected polarity.

### 5.2 TX Differential Pk-Pk Output Voltage MOI

#### **Definition:**

$V_{{\it TX-DIFFp-p}}$  (Differential Output Pk-Pk Voltage) is defined in the base specification Rev 2.0. This measurement is done using PCIe T-Tx-Diff-PP. The Result panel would display the Mean , Maximum and Minimum differential output pk-pk voltage.

#### **Test Definition Notes from the Specification:**

$$V_{TX-DIFFp-p} = 2*|V_{TX-D+} - V_{TX-D-}|$$

Measured on individual bits, first bit from a sequence in which all bits have same polarity, over specified number of UIs. The voltage measurement is referenced to the centre of each UI.

#### **Limits:**

Refer to Table 2 thru Table 11 for specified limits on the  $V_{{\it TX-DIFFp-p}}$  measurement

#### **Test Procedure:**

Ensure that *PCIe T-Tx-Diff-PP* is selected in the **Jitter and Eye diagram Analysis Tools** >> **Select** menu.

Select **Configure** >> **Clock Recovery.** Configure the Clock Recovery to be consistent with the Clock Recovery method shown in Tables 2-11.

#### **Measurement Algorithm:**

Differential Peak Voltage Measurement: The Differential Peak Voltage measurement returns two times the larger of the Min or Max statistic of the differential voltage waveform.

$$V_{DIFF-PK} = 2*Max(Max(v_{DIFF}\left(i\right));Min(v_{DIFF}\left(i\right)))$$

Where:

i is the index of all waveform values

*V*<sub>DIFF</sub> is the differential voltage signal

### 5.3 TX De-Emphasis Ratio

#### **Definition:**

V<sub>TX-DE-RATIO</sub>(De-Emphasized Differential Output Voltage (Ratio)) is defined in the base specification. This measurement uses PCIe T/nT ratio measurement.

#### **Test Definition Notes from the Specification:**

This is the ratio of the  $V_{TX-DIFFp-p}$  of the second and the following bits after a transition divided by the  $V_{TX-DIFFp-p}$  of the first bit after a transition.

#### **Limits:**

Refer to Table 2 thru Table 11 for specified limits on the  $V_{{\it TX-DIFFp-p}}$  measurement

#### **Measurement Algorithm:**

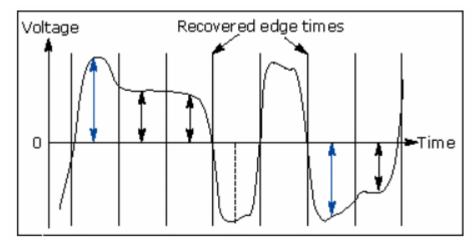

The De-emphasis Ratio measurement reports the amplitude ratio between transition and non-transition bits.

The measurement calculates the ratios of all non-transition eye voltages (2nd and subsequent eye voltages after one edge but before the next) to their nearest preceding transition eye voltage (1st eye voltage succeeding an edge). In the accompanying diagram, it is the ratio of the Black voltages to the Blue voltages. The results are given in dB.

The application calculates the T/nT Ratio using the following equations:

$$TnT(m) = dB \left( \frac{v_{EYE-HI-NTRAN}(m)}{v_{EYE-HI-TRAN}(n)} \right)$$

following a rising edge.

$$TnT(m) = dB \left( \frac{v_{EYE-LO-NTRAN}(m)}{v_{EYE-LO-TRAN}(n)} \right)$$

following a falling edge.

Where:

$v_{EYE-HI-TRAN}$  is the High voltage at the interpolated midpoint of the first unit interval following a positive transition.

$v_{EYE-LO-TRAN}$  is the Low voltage at the interpolated midpoint of the first unit interval following a negative transition.

$v_{EYE-HI-NTRAN}$  is the High voltage at the interpolated midpoint of all unit intervals except the first following a positive transition.

$v_{EYE-LO-NTRAN}$  is the Low voltage at the interpolated midpoint of all unit intervals except the first following a negative transition.

*m* is the index for all non-transition UIs.

n is the index for the nearest transition UI preceding the UI specified by m.

In a time trend plot of the measurement results, there is one measurement for each non-transition bit in the waveform (that is the black arrows in the diagram).

NOTE, PCIe T/nT Ratio measurement uses Brick Wall filter.

#### 5.4 TX Minimum Pulse Width MOI

#### **Definition:**

$T_{MIN-PULSE}$  (Instantaneous lone pulse width measurement) is defined in the base specification Rev2.0. This measurement is done using the PCIe Tmin-Pulse. The Result panel would display the minimum pulse width results.

#### **Test Definition Notes from the Specification:**

T<sub>MIN-PULSE</sub> (Instantaneous lone pulse width measurement) is measured from transition center to the next transition center, and that the transition centers will not always occur at the differential zero crossing point. In particular, transitions from a de-emphasized level to a full level will have a center point offset from the differential zero crossing.

#### **Limits:**

Refer to Table 2 thru Table 11 for specified limits on the T<sub>MIN-PULSE</sub> measurement

#### **Test Procedure:**

Ensure that *PCIe Tmin-Pulse* is selected in the Jitter and Eye diagram Analysis Tools >> Select menu.

Set the following parameters

Select **Configure** >> **Clock Recovery.** Configure the Clock Recovery to be consistent with the Clock Recovery method shown in Tables 2-11.

Configure >> General >> Off

Configure >> Global >> Off

#### **Measurement Algorithm:**

Tmin-Pulse (minimum single pulse width T<sub>Min-Pulse</sub>) is measured from one transition center to the next.

The application calculates  $T_{Min-Pulse}$  using the following equation:

$$T_{Min-Pulse} = (T_{n+1} - T_n)$$

Where:

TMin-Pulse is the minimum pulse width

T is the transition center

#### 5.5 TX Rise/Fall Time Mismatch MOI

#### **Definition:**

$T_{\text{RF-MISMATCH}}$  (Rise time, Fall time mismatch) is defined in the base specification. This measurement is done using PCIe T-RF-Mismch. The Result panel would display the Mean , Maximum and Minimum Rise time, Fall time mismatch values.

#### **Limits:**

Refer to Table 2 thru Table 11 for T<sub>RF-MISMATCH</sub> measurement.